Catena 4710 Overview

What is the Catena 4710?

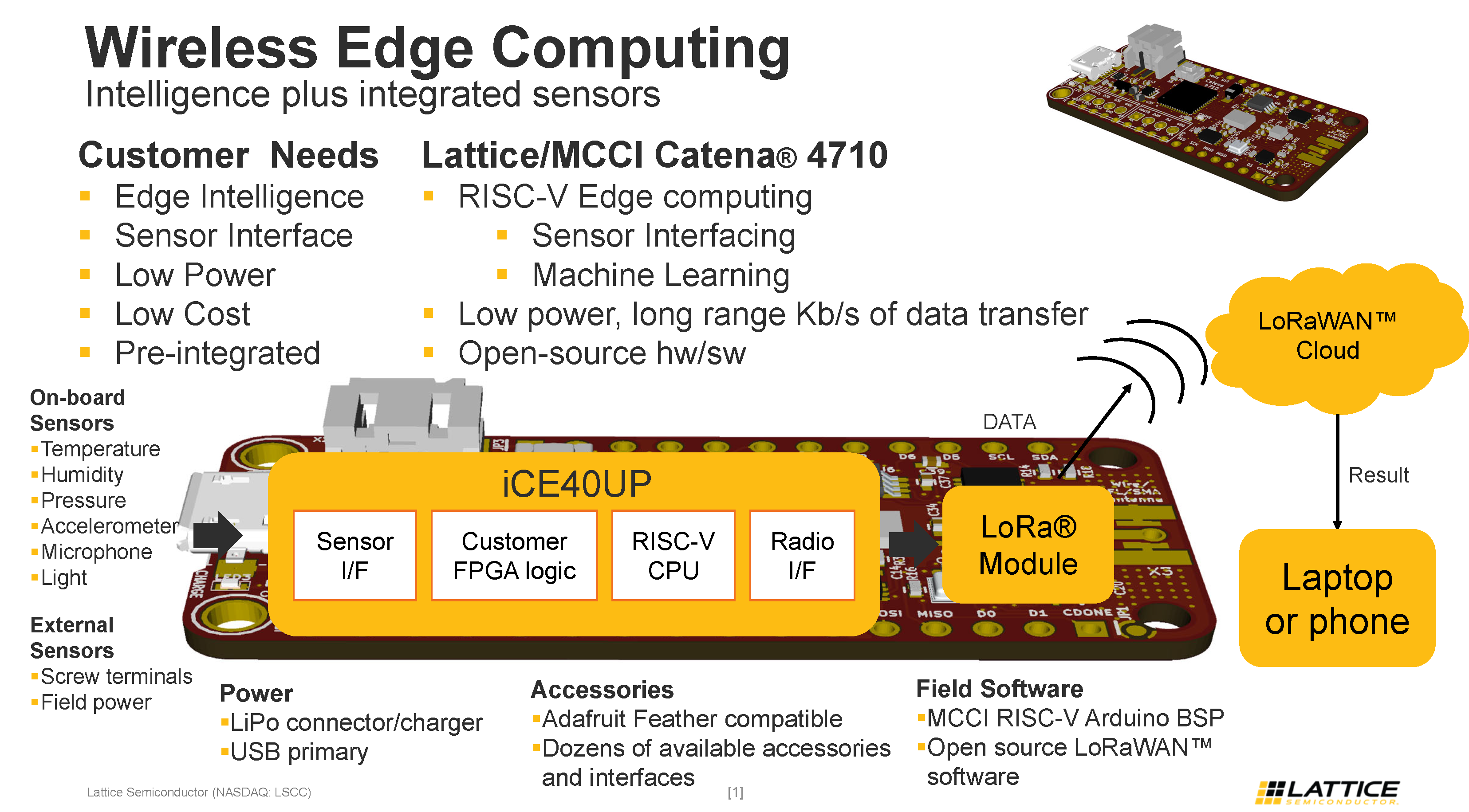

The cryptic marketing description is:

MCCI Corporation has created a combination of low-power FPGA (with RISC-V CPU) + LoRaWAN radio + sensors on a open-source single board, the Catena 4710.

If you like pictures, the cryptic marketing picture is the one MCCI and Lattice did for the trade show where we demoed the Catena 4710:

Both the text and the graphic really miss

what

the Catena 4710 is (too many abbreviations), and

why

it is. Before we can explain the why's, we probably have to give some background information.

Who's our target audience? We are targeting researchers, experimenters, teachers, students and hobbyists. We want to give them a complete system that they can use to prototype real-world IoT problems at reasonable scale (5 to 10 deployed devices). Doing this requires that we pull together a lot of different pieces and somehow integrate them.

Soft Hardware: FPGA, RTL, and related tools

Let's start with "

FPGA

". This stands for "field programmable gate array". Not much help, right? It's basically a hardware chip that can take on any personality you like, based on the program ("bitfile") you load into it. It's sort of like the microprocessors in you microwave, in that it's a deeply embedded thing; but it's radically different, in that you program at the level of gates and fops, not bits and bytes. For many years, engineers have used FPGAs to build lab prototypes of custom chips; those FPGAs are very expensive and very power hungry. More recently, Lattice Semiconductor has introduced a family of low-power devices, called the iCE40 series -- these provide fully custom hardware capabilities for milliwatts of power. If you're not into power, milliwatts is good; you can run on a battery for a while. Full FPGAs are typically more in the watts range -- you might run from a car battery for a while, but they're not suited for low-power systems.

FPGA code is developed by writing program-like text in a special kind of language, generically called a "register transfer language" (or RTL). There are two popular RTLs, Verilog and VHDL. There are, in addition, a number of higher-level variants, but chip design and FPGA design is still mostly done using an RTL. There are two flavors of RTL:

Verilog

and

VHDL

. Each language has advantages and disadvantages, but Verilog has two unfair advantages: it's the favorite in Silicon Valley, and it has much more robust open-source community. For these reasons, MCCI will be doing our FPGA code in Verilog. We want students to be able to learn skills that will make them immediately attractive to the semiconductor industry; and we need to use the open source tools as our default tool chain. (We're not religious about these choices; let a thousand flowers bloom.)

If you're writing code in Verilog, you need development tools to turn your code into something you can load into your FPGA. Lattice makes a good set of tools, but they are targeted at professional engineers; they're not supported on macOS; and some parts are most fully supported on Windows. Luckily, there is now an open-source tool chain called

Icestorm

(

link

), which allows work to be done on Windows, macOS or Linux, and which supports a debug and test model that is more friendly for casual users.

Traditional Software: RISC-V, Arduino

It has to be said: writing FPGA code is a lot more challenging than writing software. Some of that is because of the tools (and will get better with time), some of it is because of the RTL languages (which are not always intuitive), but a lot of it is because designing hardware can be hard, because of the massive parallelism. For that reason, we provide a default initial load of the FPGA, which makes it immediately useful, by turning it into a microprocessor. We're using the

RISC-V

(

link)

architecture.

RISC-V is a relatively new open-source CPU standard. If you're familiar with ARM-based processors like the STM32 or the SAMD21, you're aware that they're based on an instruction set (and core design) from ARM. Nothing wrong with that, but ARM controls the ecosystem, and that has led naturally to an open competitor (as Windows led to Linux, and cellular networks for IoT led to LoRaWAN), There are free, open-source C and C++ compilers for RISC-V. Using the default bitfile, you can immediately write software that accesses the sensors and transmits data over the LoRaWAN network.

We need a toolchain / development environment for software. Our prototype is a home-grown command-line environment using make; but researchers and students want to use the rich library of drivers and sample code available in the

Arduino

(

link)

environment. MCCI does Arduino board packages for our other products, so it's natural to plan to use that.

So, there are at least two ways to use the board. You can write software in C++ using the Arduino environment; or you can write FPGA RTL code in Verilog.

Sensors and Communication

Sensors: IoT is all about sensors; I can't think of a reason to put a system in the field without some kind of measurement interface. We included a variety of sensors on the board: temperature, pressure, humidity, light, accelerometer, microphone. We also have provision for screw terminals for connecting to a couple of external sensors (temperature probes, for example).

Communication: IoT generally requires communication from the edge node to the cloud. MCCI has been doing a lot of work with a technology called

LoRaWAN

(

link

) in the last few years. This is an open standard for using low-cost long-range LoRa radios for IoT communication. The spec covers such details as encryption, network access control, and data encapsulation. It's the basis for

The Things Network

(

link

), a global alliance of community-owned LoRaWAN networks with open access for all. By using LoRaWAN and The Things Network, researchers and students can immediately transmit data without signing up with a service provider or paying a fee. And because it's a standard with commercial network providers, there's a clear migration path when they're ready to commercialize.

Putting It All Together (the Why)

Remember, we started this long discussion promising to explain why we're doing the Catena 4710? We're finally ready to discuss it.

There is a compelling reason to combine an FPGA with sensors. For some applications, FPGAs may do a better job of turning raw measurement data into information than classic microprocessors do. The hot examples right now are based on machine learning -- you can do training off line to generate a neural network using Google's TensorFlow, then use Lattice senseAI to convert the network to an FPGA program. For example, you can train an FPGA to recognize that a face is present in front of a camera, and set a bit ("person is present") upstream to the cloud. This is much more effective than streaming raw video data to a cloud server for processing, both in terms of power consumed and in terms of communication costs.

As mentioned above, the Catena 4710 is intended to be a deployable platform for experimenting with using an FPGA in real-world applications of this kind. We want to combine all the pieces (tools, hardware, software) in an open source form that will be useful to researchers, teachers and students, without deviating too far from what is used today in industry.

Our decisions in context

Physical

: The Catena 4710 is built to Adafruit's Feather form-factor, and it's fully a Feather: it has USB and battery power, a built-in LiPo charger (for Lithium Polymer batteries), physically compatible pin-outs, and compatible voltages (3.3V). Because it's Feather-compatible, it can work with hundreds of different accessories; or it can be used to add FPGA + LoRaWAN to a standard Feather as a stackable accessory.

FPGA

: The Catena 4710 is built around a low-power Lattice FPGA, the

iCE40 Ultra Plus

(

link

). It has no extra microprocessor; all the processing is provided by the FPGA itself. MCCI provides a "soft" RISC-V core (meaning, built as an FPGA bitfile). The RISC-V uses 128k bytes of RAM that's already available inside the FPGA for program and data storage. The toolchain fully supports Verilog, and the cores provided by MCCI are written in Verilog; so they can be used for study and learning in an industry-compatible wya.

Software

: Arduino plus open-source libraries.

Communications

: We work with The Things Network as our reference LoRaWAN service.

Sensors

: we included the sensors MCCI has been using for the last two years in our IoT deployments with LoRaWAN (light, temperature, pressure, humidity), and we added a couple that seem relevant to machine learning: a six-axis accelerometer (for motion and vibration detection), and a MEMS microphone (for noise detection).

Open source:

everything is free and open source if it can be: the FPGA code, the FPGA tool chain, the schematics, the software tools, and the software we provide.

Current Status

We've built 12 units and demonstrated them at the RISC-V Summit in Santa Clara on December 4 and 5, 2018. (See

Adafruit blog post

and

Hackster.io article

.)

If you follow the links, you'll see that it's pretty real. However, we're still not done. The rev A units work well, but we have a few more things to do before it's a product.

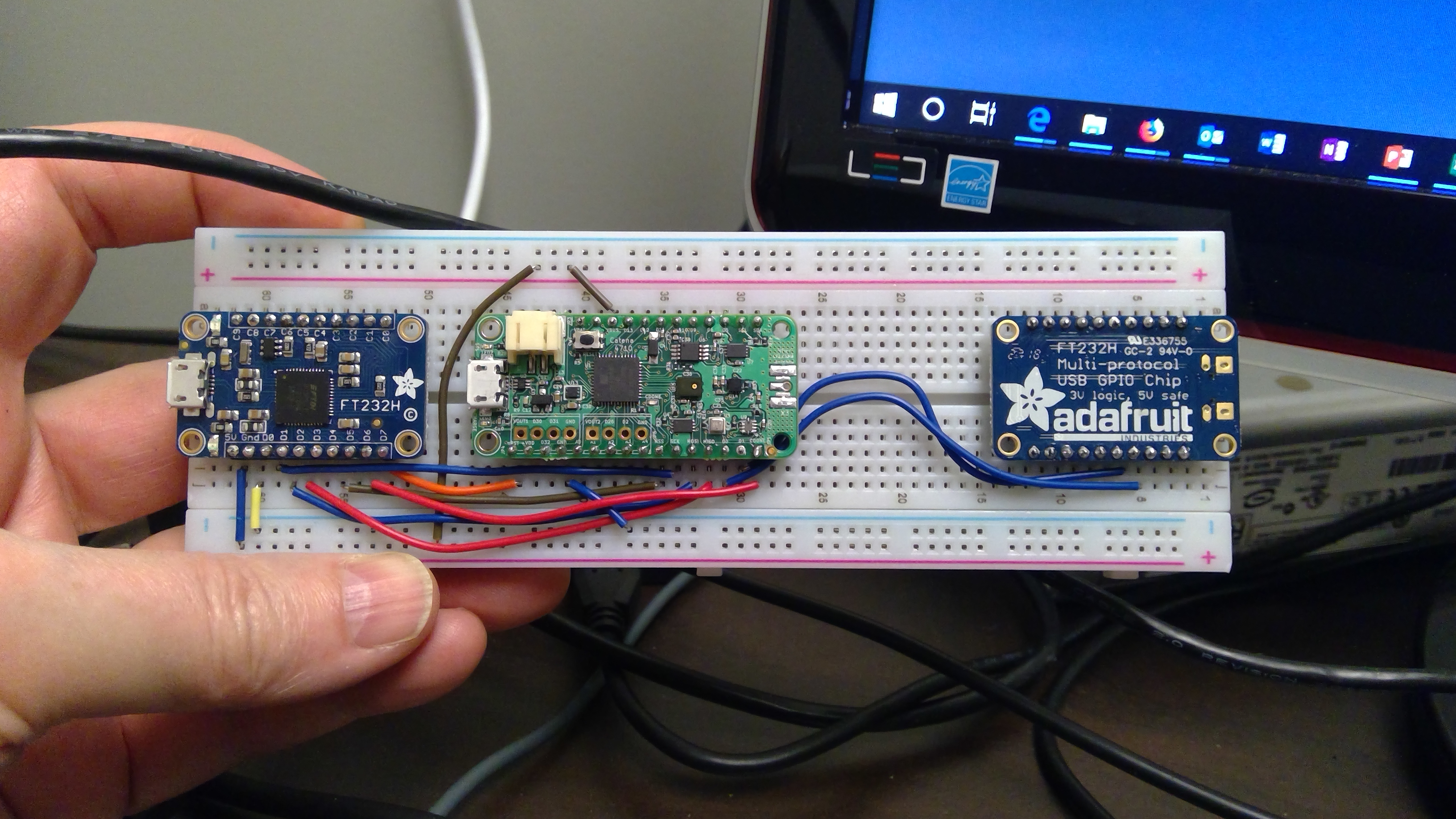

-

We need to get the USB bootloader (from TinyFPGA) working on this particular FPGAs. Right now, the USB port is only used for power; you have to use a USB-serial converter to load software, and another USB-serial converter for debug / operating I/O (see photo of breadboard below). It's not terrible, but it's kind of inconvenient. (You can also do it with clip-leads, another photo below.)

Prototyping with breadboard

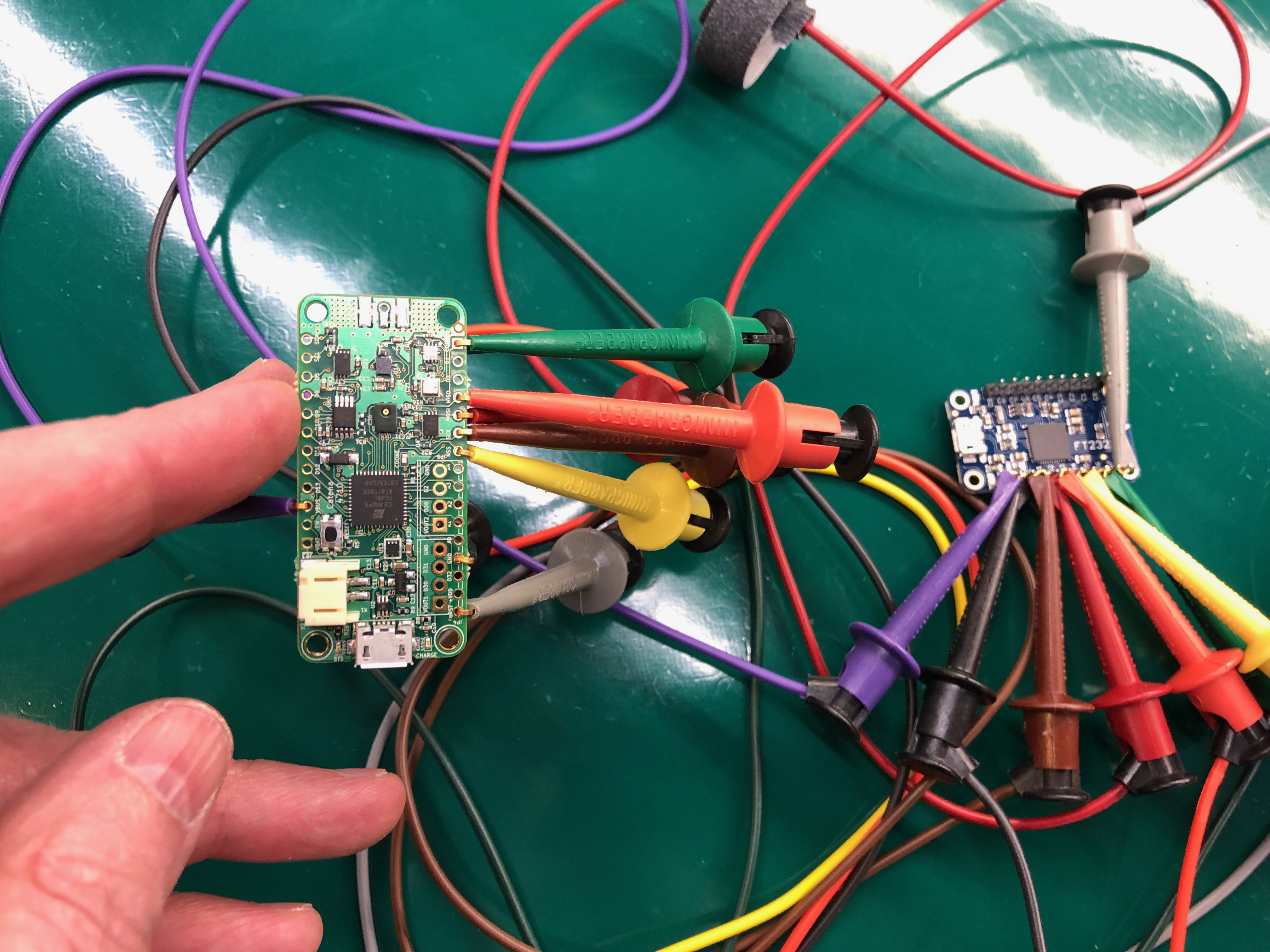

-

Prototyping with jumpers

- We need to get an official (written) release for the open-source code for the RISC-V core, from the developers. It's promised, but we can't release code until the paperwork is done.

- We need to release an Arduino environment to support software development

- We have to correct the minor glitches we've discovered in the rev A design.

- We need a manufacturing test procedure.

Things that would be nice to do, but won't delay the release:

- Come up with a curated version of the FPGA tools, possibly using PlatformIO or Apio, so that it's easy to build and download a starter app (hardware blinky).

- Build an optimized version of the RISC-V SOC core using some of the advanced features of the Lattice iCE40 Ultra Plus (like the hard SPI and I2C cores).

- Add a few missing features to the RISC-V core (particularly simple interrupts and the ability to insert breakpoints and a little more debug assist.

Based on our experience so far, it's a great little platform, but it's capabilities are so vast that MCCI will only be able to scratch the surface. The open-source strategy is helpful -- we've made, we think, a good platform for this kind of research, and the community will determine where it goes.

Price and availability -- we don't know yet! We want to sell single units for under $80; this is in the ballpark for a Feather M0 LoRa plus an external board with the required sensors and other things that are needed for real apps. We're still discussing with our fab houses. We hope to have an answer after New Years 2019. If the economics look right, we can have unit for sale about a month after we push the button.

Detailed specs

- FPGA: iCE40 Ultra Plus 5k

- Initial FPGA core

- RISC-V soft CPU core (32I instruction set) running at 6 MHz

- Built in UART and soft SPI and I2C controllers

- GPIOs

- Simple PDM to PCM converter

- 1 Mbyte flash for bitfiles and software

- Si1133 light sensor

- BME280 temperature/pressure/humidity sensor

- LIS2DS12 accelerometer

- MP34DT05 microphone

- HopeRF RFM95W LoRa radio

- 8 kbyte FRAM (non-volatile memory) for storing things like LoRaWAN link counters, session parameters and other things that may change frequently (without worrying about flash wearout)

- Feather-compatible 16-pin and 12-pin edge connector footprint

- footprint for 2 x 4 pin screw terminals, each with dedicated ground and dedicated software-controlled power

- JST-PH socket for Adafruit LiPo batteries

- LiPo charger

- Micro-B USB connector for charging and (someday) data

- ADC for monitoring VBus and VBat.

For more info

Topic Participants

Terrill Moore